1. Introduction¶

The Chromite M SoC is amongst InCore’s first No-Cost Eval SoC on FPGA based on the Chromite core generator. This SoC is targetted for IoT and Industrial class applications requiring a 64-bit micro controller.

The components of the Chromite M SoC are compliant with available RISC-V standards. The user is advised to refer to the RISC-V unprivileged , privileged and debug spec for further details.

Following is the list of currently supported FPGA boards/targets:

Arty A7 100t Amongst the cheapest development boards with sufficient space to port the current design.

1.1. Overview¶

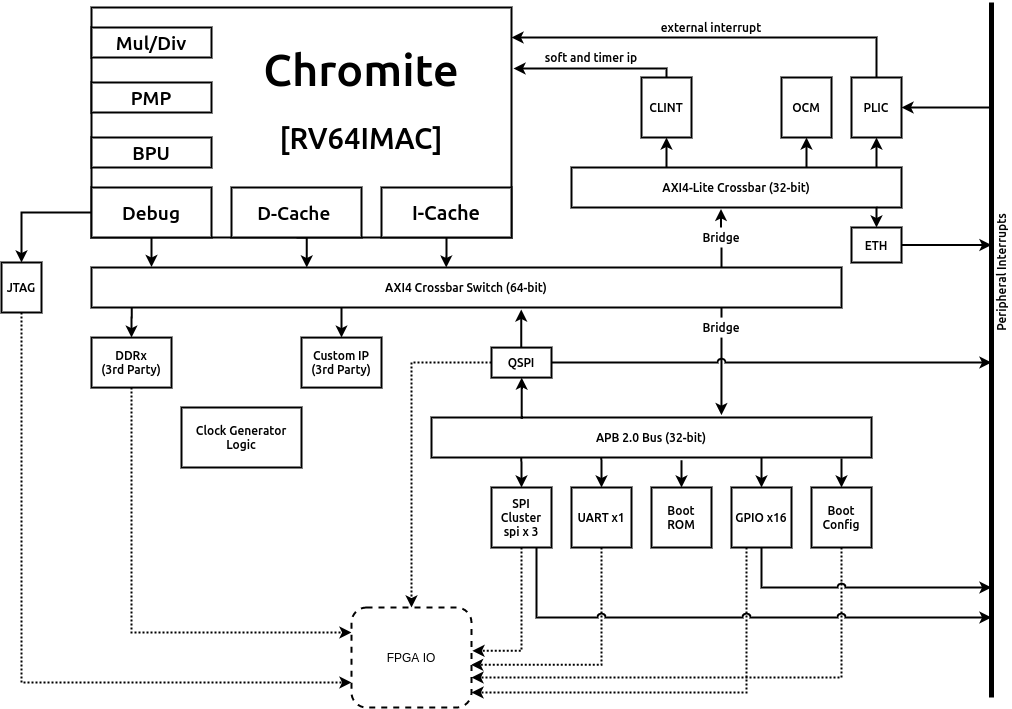

Fig. 1.1 shows the overall block diagram of the Chromite M SoC. A quick summary of the components of the SoC is available in Table 1.1

Fig. 1.1 Block diagram of the Chromite M SoC¶

Feature |

Description |

|---|---|

RISC-V Core |

The SoC uses the a 64 bit version of the Chromite core with Machine and User modes of operation only. It supports RV64IMACU extensions of the RISC-V ISA. It also includes a branch predictor, 16KiB 4 way instruction cache, 16KiB 4 way data cache and physical memory protection. Refer to Core Pipeline for more details |

PLIC |

A Platform Level Interrupt controller connected to 16 peripheral interrupts with upto 3 levels of priority. Refer to Section 18 |

UART0 |

Universal Asynchronous/Synchronous Receiver/Transmitter for serial communication Refer Section 19 for more details on this IP. |

CLINT |

Core Local Interrupt for generating software and timer interrupts. Refer to Section 17 for more details |

GPIO |

General Purpose Input/Output controller |

ROM |

Boot ROM with initial boot-code |

OCM |

BRAM based On Chip Memory. Refer to ocm for more details. |

DDRx |

A DDR IP available from the vendor (Xilinx) depending on the target FPGA. |

SPI |

A serial peripheral interface to communicate with varioud off-chip devices |

QSPI |

A quad serial peripheral interface to communicate with off-chip serial flash memories |

Debugger |

A JTAG based debugger compliant with the RISC-V debug spec v0.14. Refer to Section 13 for more details. |